开发环境:

MDK:Keil 5.30

STM32CubeMX:V6.4.0

MCU:STM32F103ZET6

6.1中断和异常

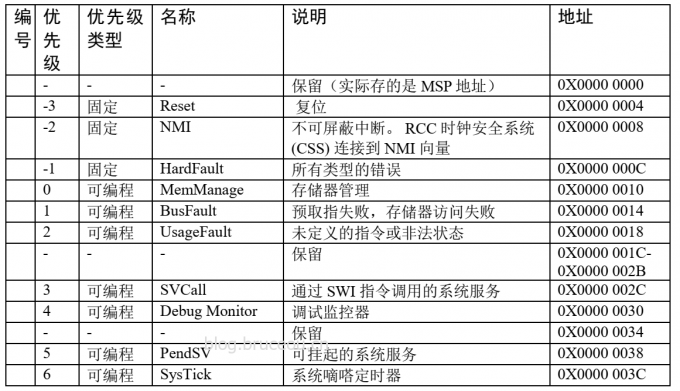

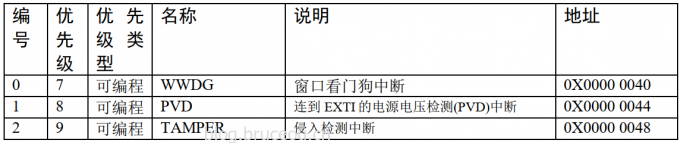

Cortex 内核具有强大的异常响应系统,它把能够打断当前代码执行流程的事件分为异常(exception)和中断(interrupt),并把它们用一个表管理起来,编号为 0 ~ 15 的称为内核异常,而 16 以上的则称为外部中断(外是相对内核而言),这个表就称为中断向量表。

STM32 对这个表重新进行了编排,把编号从 –3 至 6 的中断向量定义为系统异常,编号为负的内核异常不能被设置优先级,如复位(Reset)、不可屏蔽中断 (NMI)、硬错误(Hardfault)。从编号 7 开始的为外部中断,这些中断的优先级都是可以自行设置的。

CM3内核支持256个中断,其中 16个内核中断和240个外部中断,并具有256级可编程中断设置。STM32并没有使用CM3的全部内容,而是使用了一部分。STM32有84个中断,包括16个内核中断和68个可屏蔽中断,具有16级可编程中断优先级。STM32F103 在内核水平上搭载了一个异常响应系统, 支持为数众多的系统异常和外部中断。其中系统异常有 8 个(如果把 Reset 和 HardFault 也算上的话就是 10 个),外部中断有 60个。除了个别异常的优先级被定死外,其它异常的优先级都是可编程的。有关具体的系统异常和外部中断可在标准库文件 stm32f10x.h 这个头文件查询到,在 IRQn_Type 这个结构体里面包含了 F103 系列全部的中断和异常声明。F103 的中断和异常清单见下表。

…

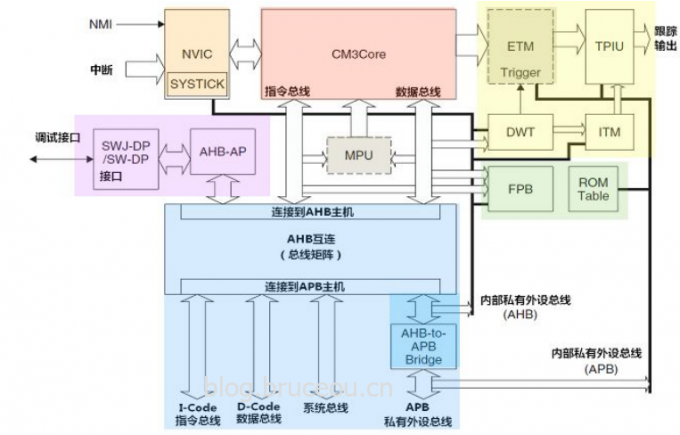

6.2 NVIC 简介

在讲如何配置中断优先级之前,我们需要先了解下中断控制器 NVIC (Nested Vectored Interrupt Controller)。 NVIC 是嵌套向量中断控制器,控制着整个芯片中断相关的功能,它跟内核紧密耦合,是内核里面的一个外设。NVIC 是属于 Cortex 内核的器件,不可屏蔽中断 (NMI)和外部中断都由它来处理,而 SYSTICK 不是由 NVIC 来控制的。

但是各个芯片厂商在设计芯片的时候会对 Cortex-M3 内核里面的 NVIC 进行裁剪,把不需要的部分去掉,所以说 STM32 的 NVIC 是 Cortex-M3 的 NVIC 的一个子集。

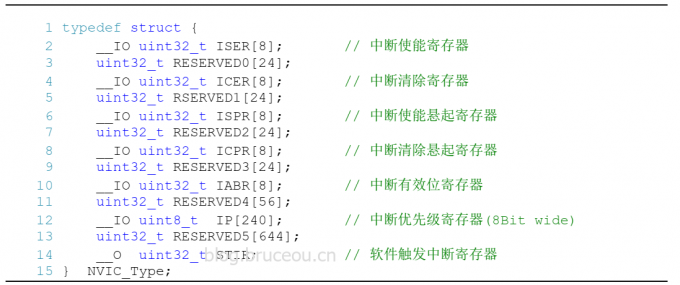

6.2.1 NVIC 寄存器简介

在固件库中, NVIC 的结构体定义可谓是颇有远虑,给每个寄存器都预留了很多位,恐怕为的是日后扩展功能。不过 STM32F103 可用不了这么多,只是用了部分而已,具体使用了多少可参考《Cortex-M3 内核编程手册》的NVIC 寄存器映射。

[ps] NVIC 结构体定义,来自固件库头文件: core_cm3.h。

在配置中断的时候我们一般只用 ISER、 ICER 和 IP 这三个寄存器, ISER 用来使能中断, ICER 用来失能中断,IP 用来设置中断优先级。

6.2.2 NVIC 中断配置固件库

固件库文件 core_cm3.h 的最后,还提供了 NVIC 的一些函数,这些函数遵循 CMSIS 规则,只要是 Cortex-M3 的处理器都可以使用,具体如下:

| NVIC 库函数 | 描述 |

|---|---|

| void NVIC_EnableIRQ(IRQn_Type IRQn) | 使能中断 |

| void NVIC_DisableIRQ(IRQn_Type IRQn) | 失能中断 |

| void NVIC_SetPendingIRQ(IRQn_Type IRQn) | 设置中断悬起位 |

| void NVIC_ClearPendingIRQ(IRQn_Type IRQn) | 清除中断悬起位 |

| uint32_t NVIC_GetPendingIRQ(IRQn_Type IRQn) | 获取悬起中断编号 |

| void NVIC_SetPriority(IRQn_Type IRQn, uint32_t priority) | 设置中断优先级 |

| uint32_t NVIC_GetPriority(IRQn_Type IRQn) | 获取中断优先级 |

| void NVIC_SystemReset(void) | 系统复位 |

这些库函数我们在编程的时候用的都比较少,甚至基本都不用。

6.3优先级的定义

6.3.1优先级定义

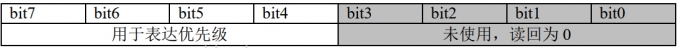

在 NVIC 有一个专门的寄存器:中断优先级寄存器 NVIC_IPRx,用来配置外部中断的优先级, IPR 宽度为 8bit,原则上每个外部中断可配置的优先级为 0~255,数值越小,优先级越高。但是绝大多数 CM3 芯片都会精简设计,以致实际上支持的优先级数减少,在F103 中,只使用了高 4bit, 如下所示:

用于表达优先级的这 4bit,又被分组成抢占优先级和子优先级。如果有多个中断同时响应,抢占优先级高的就会抢占抢占优先级低的优先得到执行,如果抢占优先级相同,就比较子优先级。如果抢占优先级和子优先级都相同的话,就比较他们的硬件中断编号,编号越小,优先级越高。

Cortex-M系列MCU的中断向量具有两个属性,一个为抢占属性,另一个为响应属性,其属性编号越小,表明它的优先级别越高。

抢占,是指打断其他中断的属性,即因为具有这个属性会出现嵌套中断(在执行中断服务函数 A 的过程中被中断 B 打断,执行完中断服务函数 B 再继续执行中断服务函数A),抢占属性由 NVIC_IRQChannelPreemptionPriority 的参数配置。

而响应属性则应用在抢占属性相同的情况下,当 两个中断向量的抢占优先级相同时,如 果两个中断同时到达,则先处理响应优先级高的中断,响应属性 由NVIC_IRQChannelSubPriority 参数配置。例如,现在有三个中断向量,见下表。

| 中断向量 | 抢占优先级 | 响应优先级 |

|---|---|---|

| A | 0 | 0 |

| B | 1 | 0 |

| C | 1 | 1 |

若内核正在执行 C 的中断服务函数,则它能被抢占优先级更高的中断 A 打断,由于 B和 C 的抢占优先级相同,所以 C 不能被 B 打断。但如果 B 和 C 中断是同时到达的,内核就会首先响应响应优先级别更高的 B 中断。

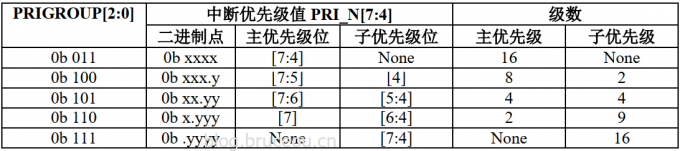

6.3.2优先级分组

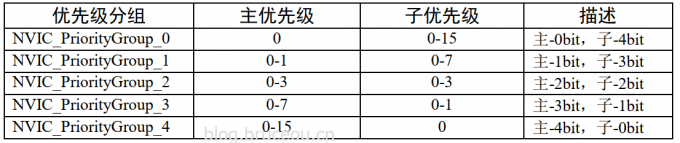

优先级的分组由内核外设 SCB 的应用程序中断及复位控制寄存器 AIRCR 的PRIGROUP[10:8]位决定, F103 分为了 5 组,具体如下:主优先级=抢占优先级。

设置优先级分组可调用库函数 NVIC_PriorityGroupConfig()实现,有关 NVIC 中断相关的库函数都在库文件 misc.c 和 misc.h 中。

/**

* 配置中断优先级分组:抢占优先级和子优先级

* 形参如下:

* @arg NVIC_PriorityGroup_0: 0bit for 抢占优先级

* 4 bits for 子优先级

* @arg NVIC_PriorityGroup_1: 1 bit for 抢占优先级

* 3 bits for 子优先级

* @arg NVIC_PriorityGroup_2: 2 bit for 抢占优先级

* 2 bits for 子优先级

* @arg NVIC_PriorityGroup_3: 3 bit for 抢占优先级

* 1 bits for 子优先级

* @arg NVIC_PriorityGroup_4: 4 bit for 抢占优先级

* 0 bits for 子优先级

* @注意 如果优先级分组为 0,则抢占优先级就不存在,优先级就全部由子优先级控制

*/

void NVIC_PriorityGroupConfig(uint32_t NVIC_PriorityGroup)

{

// 设置优先级分组

SCB->AIRCR = AIRCR_VECTKEY_MASK | NVIC_PriorityGroup;

}

在配置优先级的时候,还要注意一个很重要的问题,即中断种类的数量。NVIC 只可以配置 16 种中断向量的优先级,也就是说,抢占优先级和响应优先级的数量由一个 4 位的数字来决定,把这个 4 位数字的位数分配成抢占优先级部分和响应优先级部分。有 5 组分配方式 :

第 0 组: 所有 4 位用来配置响应优先级。即 16 种中断向量具有都不相同的响应优先级。

第 1 组:最高 1 位用来配置抢占优先级,低 3 位用来配置响应优先级。表示有 21=2 种级别的抢占优先级(0 级,1 级),有 23=8 种响应优先级,即在 16 种中断向量之中,有8 种中断,其抢占优先级都为 0 级,而它们的响应优先级分别为 0~7,其余 8 种中断向量的抢占优先级则都为 1 级,响应优先级别分别为 0~7。

第 2 组:2 位用来配置抢占优先级,2 位用来配置响应优先级。即 22=4 种抢占优先级,22=4 种响应优先级。

第 3 组:高 3 位用来配置抢占优先级,最低 1 位用来配置响应优先级。即有 8 种抢占优先级,2 种响应 2 优先级。

第 4 组:所有 4 位用来配置抢占优先级,即 NVIC 配置的 24 =16 种中断向量都是只有抢占属性,没有响应属性。

要配置这些优先级组,可以采用库函数 NVIC_PriorityGroupConfi g(),可输入的参数为NVIC_PriorityGroup_0 ~ NVIC_PriorityGroup_4,分别为以上介绍的 5 种分配组。

6.3.3中断编程

在配置每个中断的时候一般有 3 个编程要点:

1、使能外设某个中断,这个具体由每个外设的相关中断使能位控制。比如串口有发送完成中断,接收完成中断,这两个中断都由串口控制寄存器的相关中断使能位控制。

2、初始化 NVIC_InitTypeDef 结构体,配置中断优先级分组,设置抢占优先级和子优先级,使能中断请求。 NVIC_InitTypeDef 结构体在固件库头文件 misc.h 中定义。

typedef struct {

uint8_t NVIC_IRQChannel; // 中断源

uint8_t NVIC_IRQChannelPreemptionPriority; // 抢占优先级

uint8_t NVIC_IRQChannelSubPriority; // 子优先级

FunctionalState NVIC_IRQChannelCmd; // 中断使能或者失能

} NVIC_InitTypeDef;有关 NVIC 初始化结构体的成员我们一一解释下:

1) NVIC_IROChannel:用来设置中断源,不同的中断中断源不一样,且不可写错,即使写错了程序也不会报错,只会导致不响应中断。具体的成员配置可参考 stm32f10x.h 头文件里面的 IRQn_Type 结构体定义,这个结构体包含了所有的中断源。

typedef enum IRQn {

//Cortex-M3 处理器异常编号

NonMaskableInt_IRQn = -14,

MemoryManagement_IRQn = -12,

BusFault_IRQn = -11,

UsageFault_IRQn = -10,

SVCall_IRQn = -5,

DebugMonitor_IRQn = -4,

PendSV_IRQn = -2,

SysTick_IRQn = -1,

//STM32 外部中断编号

WWDG_IRQn = 0,

PVD_IRQn = 1,

TAMP_STAMP_IRQn = 2,

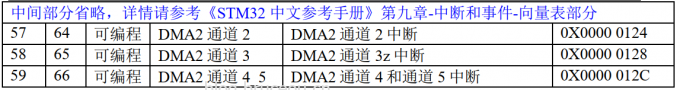

//限于篇幅,中间部分代码省略,具体的可查看库文件 stm32f10x.h

DMA2_Channel2_IRQn = 57,

DMA2_Channel3_IRQn = 58,

DMA2_Channel4_5_IRQn = 59

} IRQn_Type;2) NVIC_IRQChannelPreemptionPriority:抢占优先级,具体的值要根据优先级分组来确定,具体参考表6优先级分组真值表 。

3) NVIC_IRQChannelSubPriority:子优先级,具体的值要根据优先级分组来确定,具体参考表6优先级分组真值表 。

4) NVIC_IRQChannelCmd:中断使能( ENABLE)或者失能( DISABLE)。操作的是 NVIC_ISER 和 NVIC_ICER 这两个寄存器。

3、编写中断服务函数

在启动文件 startup_stm32f10x_hd.s 中我们预先为每个中断都写了一个中断服务函数,只是这些中断函数都是为空,为的只是初始化中断向量表。实际的中断服务函数都需要我们重新编写,为了方便管理我们把中断服务函数统一写在 stm32f10x_it.c 这个库文件中。关于中断服务函数的函数名必须跟启动文件里面预先设置的一样,如果写错,系统就在中断向量表中找不到中断服务函数的入口,直接跳转到启动文件里面预先写好的空函数,并且在里面无限循环,实现不了中断。

欢迎访问我的网站

BruceOu的哔哩哔哩

BruceOu的主页

BruceOu的博客

BruceOu的CSDN博客

BruceOu的简书

BruceOu的知乎

欢迎订阅我的微信公众号

关注公众号[嵌入式实验楼]获取更多资讯